# **ADQ3-FWATD Datasheet**

The ADQ3-FWATD is an averaging firmware of the high-end ADQ3 series of digitizers. The FWATD is designed to maximize the signal to noise ratio in pulse data systems.

# **Ordering information**

ADQ3 digitizer including firmware FWATD, order code ADQ3-FWATD.

# **Compatible hardware models**

- ADQ30 single-channel mode

- ADQ32 single- and dual-channel modes

- ADQ32-PDRX combined channels and dual-channel mode (not combined)

- ADQ33 dual-channel mode

- ADQ33-PDRX combined channels and dual-channel mode (not combined)

- ADQ35 single- and dual-channel mode

# L ADQ3-FWATD INTRODUCTION

#### 1.1 Features

- Accumulation of waveforms at high duty cycle

- Background streaming of data, no dead-time between accumulation

- DBS digital baseline stabilizer to reduce pattern noise

- Digital FIR filter for bandwidth limitation

- Sample skip support to increase measurement length

- Threshold function for suppressing noise

- FIR filter for threshold control enables pulse shape selection

- Dual gain PDRX firmware in combination with averaging (separate license may apply)

# 1.2 Applications

- Time-of-flight Mass Spectrometry

- Distributed Optical Fiber Sensing

- Noise reduction of repetitive measurements

- Pulse data applications

# 1.3 Advantages

- Efficient implementation of averaging in the FPGA off-loading the PC

- Four noise reduction methods

- Digital Baseline Stabilizer (DBS)

- o FIR filter for noise filtering

- o Threshold for noise cancellation

- Averaging for noise reduction

- Optimized for real-time processing and high data throughput

- Teledyne SP Devices' design services are available for fast integration to reduce time-tomarket

#### 2 FOUR NOISE SUPPRESSION METHODS – PRINCIPLE OF OPERATION

## 2.1 DBS - Digital Baseline Stabilizer

The DBS analyses the signal and subtracts DC offset. This creates a solid reference point for computing pulse-related parameters. The DBS actively compensates for slow baseline shifts as temperature variations, supply voltage drift and aging and stabilizes the baseline to a level corresponding to 22 bits precision.

The DBS also compensates for pattern noise in interleaved ADCs. This is important when averaging very long sequences since the pattern noise may drown weak signals.

## 2.2 General purpose FIR filter

The general-purpose FIR filter enables the suppression of noise in a certain frequency band. The FIR filter is user-controlled so that it can be optimized for the specific application/system.

## 2.3 Threshold with FIR filter

Threshold operation sets samples below a user-defined level, t, to a user-controlled register value, z, (often 0). The threshold function can be tuned with a filter to emphasize certain pulse shapes by the threshold filter function. The operation is like follows:

- 1. The sequence of samples is  $[x_0 x_1 x_2 ... x_n]$ .

- 2. Apply the threshold filter on the sequence of sample to get  $[f_0 f_1 f_2 ... f_n]$ .

- 3. The conditions are then:

- a. for each sample f which is below the threshold t, set register value z.

- b. for each sample f which is above the threshold t, maintain the value of x.

This example is for positive signals. The threshold operation works for both negative and positive signals.

## 2.4 Accumulator

The accumulator adds records (waveforms) to each other. The noise is assumed to be uncorrelated and the signal is assumed to be correlated. The accumulation then enhances the signal to noise ratio. An example of operation is:

The first record,  $r_0$ , contains the series of samples [ $x_{00} x_{01} x_{02} ... x_{0n}$ ], where  $x_{00}$  is the first sample. Following records are  $r_1 = [x_{10} x_{11} x_{12} ... x_{1n}]$  and  $r_2 = [x_{20} x_{21} x_{22} ... x_{2n}]$ . The accumulator result for adding these records is then the series [ $(x_{00}+x_{10}+x_{20})(x_{01}+x_{11}+x_{21})(x_{02}+x_{12}+x_{22})...(x_{0n}+x_{1n}+x_{2n})$ ].

If the division part of the averaging function is required, it must be implemented in the user's application software.

#### 3 SYSTEM DESIGN USING FWATD

#### 3.1 Fundamental observations

The environment where FWATD is used is a real-time operating measurement system. The signals detector and the digitizer operate in a real-time domain. The data is analyzed in a PC, which is not real-time controlled. Certain design steps have been taken in the FWATD to handle the transition for the real-time domain into the PC in a safe way.

#### 3.2 System design optimization; open FPGA and streaming to CPU and GPU

High-performance data acquisition systems require high speed real-time analysis. ADQ3-series offers a variety of options for efficient system design:

The FWATD firmware implements the most demanding core of the processing in the FPGA. Data from the processing is streamed to a PC using the high-speed streaming interface.

The streaming of data proceeds in parallel with the recording. There is thus no dead-time introduced by data transfer.

There are many parameters to tune for optimal performance. See the ADQ3 series user guide for instructions.

## 3.3 Scheduling for high performance and data safety

The FWATD is suitable for a system with a strict scheduled operation. The dataflow is driven by the trigger, internal from the digitizer or external from the signal source. The user must make sure that all data transport and processing is fast enough to handle the data rate.

The FWATD firmware is designed to operate constantly over long time in a system which maximizes the performance. The FWATD firmware contains multiple features to support the data transport and processing.

- 1. There is a FIFO on the digitizer to manage unexpected interrupts in the PCIe data transport.

- 2. There is a controlled data discard in case of an overflow due to interrupts anywhere in the processing chain.

- 3. There is an auto-recover and re-synchronize feature in case of lost data. This is useful for very long measurement operations. In case of an unexpected interrupt in the data transport which cannot be handled by the FIFO, the FWATD firmware maintains the grid established by the trigger source and the accumulation factor and ensures that the following accumulations are not affected. It is not necessary to restart the system to continue the measurement.

- 4. The data read-out is thread safe and multiple threads can operate on the data. This increases the processing capacity of the system.

# 4 TECHNICAL DATA

# **Table 1 Software support**

| Parameter                     | Value              |  |

|-------------------------------|--------------------|--|

| Operating system <sup>1</sup> | Windows 10 / Linux |  |

| GUI                           | Digitizer Studio   |  |

| Example code                  | C, Python          |  |

| API                           | C / C++            |  |

## **Table 2 Hardware models**

| Digitizer model | Sampling rate per channel | Channels | Max Record<br>length <sup>2</sup> | Max data<br>transfer rate <sup>3 4</sup> |

|-----------------|---------------------------|----------|-----------------------------------|------------------------------------------|

| ADQ33           | 1 GSPS                    | 2        | 500 ms                            | 7 GBPS                                   |

| ADQ33-PDRX      | 1 GSPS                    | 1        | 500 ms                            | 7 GBPS                                   |

| ADQ33-PDRX      | 1 GSPS                    | 2        | 500 ms                            | 7 GBPS                                   |

| ADQ32           | 2.5 GSPS                  | 2        | 200 ms                            | 7 GBPS                                   |

| ADQ32           | 5 GSPS                    | 1        | 200 ms                            | 7 GBPS                                   |

| ADQ32-PDRX      | 2.5 GSPS                  | 1        | 200 ms                            | 7 GBPS                                   |

| ADQ32-PDRX      | 2.5 GSPS                  | 2        | 200 ms                            | 7 GBPS                                   |

| ADQ30           | 1 GSPS                    | 1        | 500 ms                            | 7 GBPS                                   |

| ADQ35           | 5 GSPS                    | 2        | 200 us                            | 14 GBPS                                  |

| ADQ35           | 10 GSPS                   | 1        | 200 us                            | 14 GBPS                                  |

<sup>&</sup>lt;sup>1</sup> See 15-1494 Operating system support for a detailed listing of supported distributions.

<sup>&</sup>lt;sup>2</sup> If sample skip is used the record length is increased in the same degree as samples are skipped.

<sup>&</sup>lt;sup>3</sup> This is the rate supported by the digitizer hardware. The effective data rate may be limited by components in the system.

<sup>&</sup>lt;sup>4</sup> Using averaging reduces the actual data rate. The data rate can be approximated as trigger\_rate [Hz] \* record\_length [samples] \* 4 [bytes/sample] / number of accumulations.

## **Table 3 General parameters**

| Parameter                                       | Min         | Max     | Unit |

|-------------------------------------------------|-------------|---------|------|

| FIR filter general purposes 5                   | 1           | 17      | taps |

| FIR filter for threshold operation <sup>5</sup> | 1           | 17      | taps |

| Number of accumulations <sup>6</sup>            | 1           | 262 144 |      |

| Re-arm time between records <sup>7</sup>        | 20          |         | ns   |

| Dead time between accumulations <sup>7</sup>    | 20          |         | ns   |

| Data format                                     | 8 / 16 / 32 |         | bits |

## 5 CHANGING NUMBER OF CHANNELS

Some hardware models support both one and 2 channels operation. Changing from 2 channels to 1 channel is done by changing firmware image in the FPGA. Both firmware images are stored in the non-volatile memory of the digitizer. Use the software tool ADQAssist to change boot image. Changing firmware requires power cycling of the PC for the PCle bus to enumerate.

<sup>&</sup>lt;sup>5</sup> The filter is symmetrical so there are 9 unique coefficients.

<sup>&</sup>lt;sup>6</sup> This is limited by the 32-bit data format from the digitizer. Since the accumulations are seamless, the user can convert data to 64-bit format and continue the accumulation to almost any number of records.

<sup>&</sup>lt;sup>7</sup> Re-arm time between records are well as dead-time between accumulations is 20ns. This means that a new accumulation can be started seamlessly without any loss of data. If the number of accumulations is small, an increased dead-time may be necessary to meet the data transfer requirements.

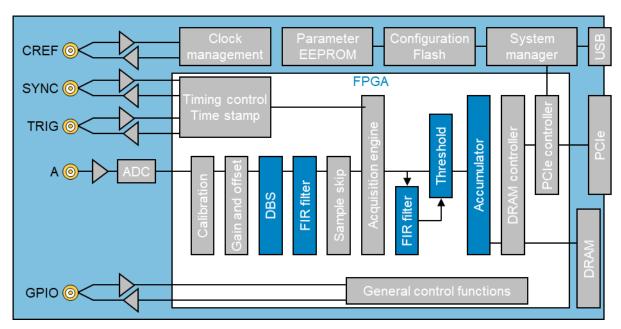

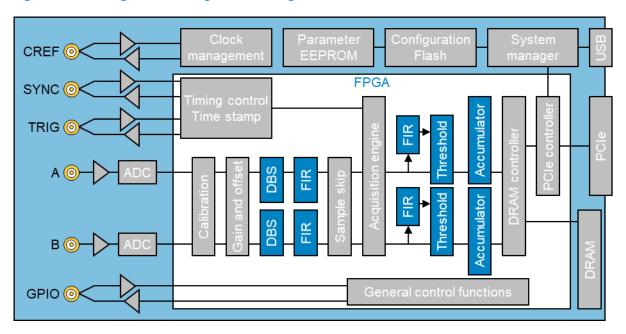

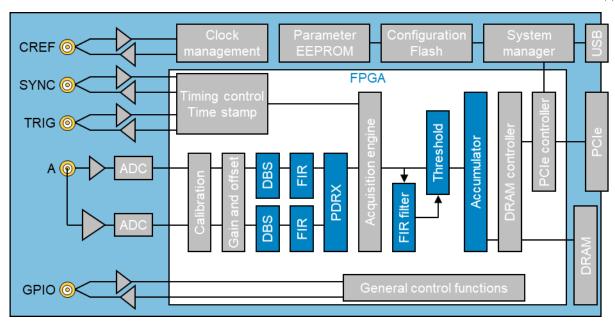

# 6 BLOCK DIAGRAM

Figure 1 Block diagram for a single channel digitizer.

Figure 2 Block diagram for a dual channel digitizer

Figure 3 Combined with PDRX (requires PDRX license)

Figure 4 Typical digitizer in the ADQ3 family

## **Important Information**

Teledyne Signal Processing Devices Sweden AB (Teledyne SP Devices) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to Teledyne SP Devices' general terms and conditions supplied at the time of order acknowledgment.

Teledyne SP Devices warrants that each product will be free of defects in materials and workmanship, and conform to specifications set forth in published data sheets, for a period of three (3) years. The warranty commences on the date the product is shipped by Teledyne SP Devices. Teledyne SP Devices' sole liability and responsibility under this warranty is to repair or replace any product which is returned to it by Buyer and which Teledyne SP Devices determines does not conform to the warranty. Product returned to Teledyne SP Devices for warranty service will be shipped to Teledyne SP Devices at Buyer's expense and will be returned to Buyer at Teledyne SP Devices' expense. Teledyne SP Devices will have no obligation under this warranty for any products which (i) has been improperly installed; (ii) has been used other than as recommended in Teledyne SP Devices' installation or operation instructions or specifications; or (iii) has been repaired, altered or modified by entities other than Teledyne SP Devices. The warranty of replacement products shall terminate with the warranty of the product. Buyer shall not return any products for any reason without the prior written authorization of Teledyne SP Devices.

In no event shall Teledyne SP Devices be liable for any damages arising out of or related to this document or the information contained in it.

TELEDYNE SP DEVICES' EXPRESS WARRANTY TO BUYER CONSTITUTES TELEDYNE SP DEVICES' SOLE LIABILITY AND THE BUYER'S SOLE REMEDY WITH RESPECT TO THE PRODUCTS AND IS IN LIEU OF ALL OTHER WARRANTIES, LIABILITIES AND REMEDIES. EXCEPT AS THUS PROVIDED, TELEDYNE SP DEVICES DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT.

TELEDYNE SP DEVICES DOES NOT INDEMNIFY, NOR HOLD THE BUYER HARMLESS, AGAINST ANY LIABILITIES, LOSSES, DAMAGES AND EXPENSES (INCLUDING ATTORNEY'S FEES) RELATING TO ANY CLAIMS WHATSOEVER. IN NO EVENT SHALL TELEDYNE SP DEVICES BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, INCLUDING LOST PROFIT, LOST DATA AND THE LIKE, DUE TO ANY CAUSE WHATSOEVER. NO SUIT OR ACTION SHALL BE BROUGHT AGAINST TELEDYNE SP DEVICES MORE THAN ONE YEAR AFTER THE RELATED CAUSE OF ACTION HAS ACCRUED. IN NO EVENT SHALL THE ACCRUED TOTAL LIABILITY OF TELEDYNE SP DEVICES FROM ANY LAWSUIT, CLAIM, WARRANTY OR INDEMNITY EXCEED THE AGGREGATE SUM PAID TO SP BY BUYER UNDER THE ORDER THAT GIVES RISE TO SUCH LAWSUIT, CLAIM, WARRANTY OR INDEMNITY.

## **Worldwide Sales and Technical Support**

www.spdevices.com

# **Teledyne SP Devices Corporate Headquarters**

Teknikringen 8 SE-583 30 Linköping Sweden

Phone: +46 (0)13 465 0600 Fax: +46 (0)13 991 3044 Email: <u>info@spdevices.com</u>

Copyright © 2024 Teledyne Signal Processing Devices Sweden AB. All rights reserved, including those to reproduce this publication or parts thereof in any form without permission in writing from Teledyne SP Devices.